## User Guide v-1

# Circuit Solver User Guide

# Contents

| 1        | Inti | oducti | ion                               | 1  |

|----------|------|--------|-----------------------------------|----|

|          | 1.1  | Featur | res                               | 1  |

|          | 1.2  |        | lation                            | 2  |

|          | 1.3  |        | sing                              | 2  |

|          |      | 1.3.1  | Purchasing the licenses           | 3  |

|          |      | 1.3.2  | Node-locked license activation    | 4  |

|          |      | 1.3.3  | Server license activation         | 5  |

|          |      | 1.3.4  | Testing                           | 5  |

| <b>2</b> | Lin  | ear Co | omponents                         | 7  |

|          | 2.1  |        | ve Components                     | 7  |

|          |      | 2.1.1  | Resistor                          | 7  |

|          |      | 2.1.2  | Inductor                          | 8  |

|          |      | 2.1.3  | Mutual inductance                 | 8  |

|          |      | 2.1.4  | Capacitor                         | 9  |

|          | 2.2  | Active | e components                      | 9  |

|          |      | 2.2.1  | Voltage source                    | 9  |

|          |      | 2.2.2  | Current source                    | 10 |

|          |      | 2.2.3  | Transient waveform shapes         | 10 |

|          | 2.3  | Depen  | ndent sources                     | 11 |

|          |      | 2.3.1  | Voltage-controlled voltage source | 11 |

|          |      | 2.3.2  | Voltage-controlled Current source | 12 |

|          |      | 2.3.3  | Current-controlled voltage source | 13 |

|          |      | 2.3.4  | Current-controlled current source | 14 |

|          | 2.4  | Switch |                                   | 15 |

|          |      | 2.4.1  | Voltage-controlled switch         | 15 |

iv CONTENTS

|   |     | 2.4.2 Current-controlled switch         | 16         |

|---|-----|-----------------------------------------|------------|

|   | 2.5 | Transmission line models                | 16         |

|   |     |                                         | 16         |

|   |     |                                         | 18         |

|   |     |                                         | 20         |

| 3 | Tra | nsfer-function or state-space models    | 21         |

|   | 3.1 | <u>-</u>                                | 21         |

|   | 3.2 |                                         | 22         |

|   | 3.3 |                                         | 22         |

|   |     |                                         | 23         |

|   |     |                                         | 24         |

| 4 | Noi | n-linear Components                     | 25         |

| _ | 4.1 | 1                                       | 25         |

|   | 4.2 |                                         | 28         |

|   | 4.3 |                                         | 33         |

|   | 4.4 | ±                                       | 37         |

|   | 4.5 |                                         | 12         |

| 5 | Sub | ocircuits and Parametric Equations 4    | 17         |

| 0 | 5.1 |                                         | <b>4</b> 9 |

|   | 0.1 |                                         | 49         |

| 6 | The | ermal Circuit Solver                    | 51         |

| Ů | 6.1 |                                         | 51         |

|   | 0.1 | r                                       | 52         |

|   |     |                                         | 52         |

|   |     | - · · · · · · · · · · · · · · · · · · · | 53         |

|   |     | 0                                       | 53         |

|   | 6.2 |                                         | 53         |

|   | 6.3 |                                         | 54         |

|   | 6.4 |                                         | 55         |

| 7 | Pvt | hon Interface                           | 59         |

| • | 7.1 |                                         | 30         |

|   | 7.2 | 1 10 1                                  | 31         |

|   | 7.3 |                                         | 32<br>32   |

CONTENTS v

|    | 7.4  | Add Analyses                                      | 63 |

|----|------|---------------------------------------------------|----|

|    | 7.5  | Read Solution Data                                | 64 |

| 8  | Fun  | ctional Modeling of The Driver Chip               | 67 |

|    | 8.1  | Defining the functional model                     | 67 |

|    |      | 8.1.1 Defining the model class                    | 69 |

|    |      | 8.1.2 Creating the driver instance                | 69 |

|    |      | 8.1.3 Creating the driver in the netlist file     | 70 |

|    |      | 8.1.4 Linking the functional model to the driver  | 70 |

|    | 8.2  | Python model library file                         | 71 |

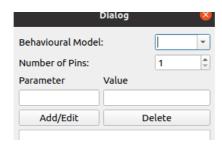

| 9  | Beh  | avioural Model Interface                          | 73 |

|    | 9.1  | Defining the behavioural model                    | 73 |

|    |      | 9.1.1 Behavioural model class definition          | 73 |

|    |      | 9.1.2 Use of auto-differentiation                 | 76 |

|    |      | 9.1.3 Example code                                | 76 |

|    |      | 9.1.4 Linking the behavioural model to the driver | 78 |

|    | 9.2  | Python model library file                         | 78 |

| 10 | Circ | cuit Analyses                                     | 81 |

|    | 10.1 | DC analysis                                       | 81 |

|    | 10.2 | AC analysis                                       | 82 |

|    | 10.3 | Transient analysis                                | 83 |

|    |      | 10.3.1 Time-stepping                              | 84 |

|    | 10.4 | Solver settings                                   | 84 |

| 11 | Circ | cuit Netlist File Format                          | 87 |

|    | 11.1 | Circuit File structure                            | 87 |

|    | 11.2 | Output files                                      | 89 |

| 12 | Line | ear Circuit simulation                            | 91 |

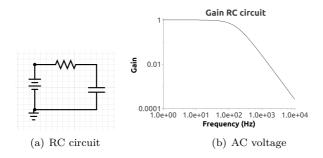

|    | 12.1 | R-C circuits                                      | 91 |

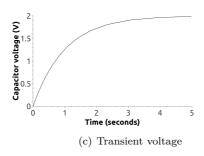

|    | 12.2 | L-R circuits                                      | 93 |

|    |      | R-L-C circuits                                    | 93 |

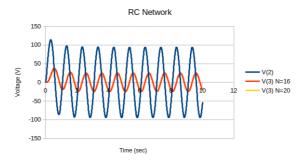

|    |      | RC-networks                                       | 96 |

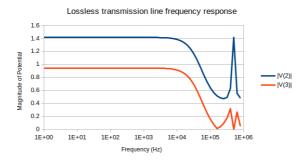

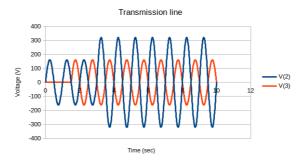

|    |      | Lossless TL                                       | 98 |

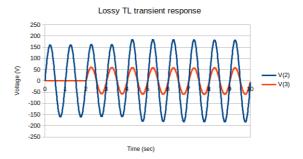

|    |      | Lossy TL                                          | 98 |

vi CONTENTS

| 13 |      |         | Circuit simulation            | 101 |

|----|------|---------|-------------------------------|-----|

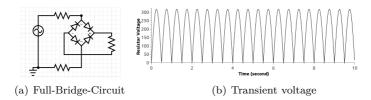

|    | 13.1 | Full-br | ridge rectifier               | 101 |

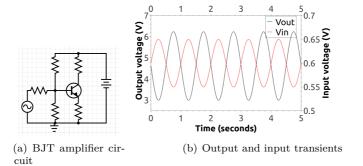

|    | 13.2 | BJT a   | mplifier                      | 102 |

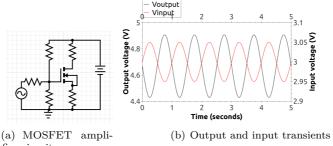

|    | 13.3 | MOSF    | ET amplifier                  | 104 |

| 14 | Circ | cuit Op | ptimization                   | 107 |

|    | 14.1 |         | nizer functions               | 107 |

|    |      | 14.1.1  | Initialize                    | 107 |

|    |      | 14.1.2  | Setup optimizer               | 108 |

|    |      | 14.1.3  | Optimize                      | 111 |

|    | 14.2 | Examp   | ple Code                      | 112 |

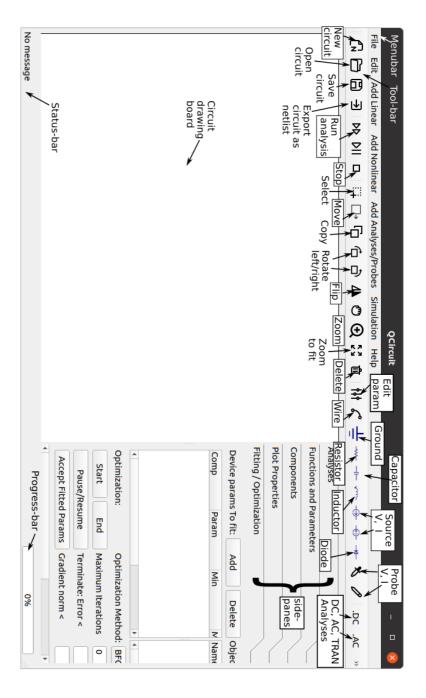

| 15 | Circ | cuit Dr | rawing Application            | 115 |

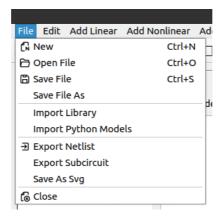

|    |      |         | ienu                          | 117 |

|    |      |         | New                           | 117 |

|    |      |         | Open File                     | 117 |

|    |      |         | Save File                     | 118 |

|    |      |         | Save File As                  | 118 |

|    |      |         | Import Library                | 118 |

|    |      | 15.1.6  | Import Python Models          | 118 |

|    |      |         | Export Netlist                | 119 |

|    |      |         | Export Subcircuit             | 119 |

|    |      | 15.1.9  | Save As Svg                   | 119 |

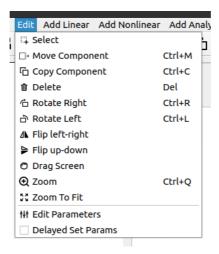

|    | 15.2 | Edit-m  | nenu                          | 119 |

|    |      |         | Select                        | 119 |

|    |      |         | Move Component                | 120 |

|    |      |         | Copy Component                | 120 |

|    |      |         | Delete                        | 121 |

|    |      |         | Rotate Right/Left             | 121 |

|    |      | 15.2.6  | Flip Up-down/Right-left       | 121 |

|    |      | 15.2.7  |                               | 121 |

|    |      | 15.2.8  |                               | 121 |

|    |      | 15.2.9  | Zoom to fit                   | 122 |

|    |      |         | OEdit Parameters              | 122 |

|    |      |         | 1 Delayed Set Params          | 122 |

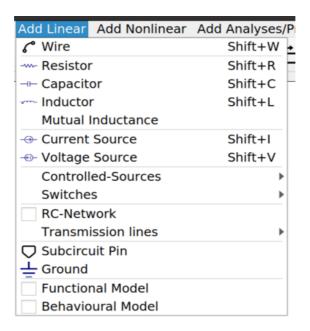

|    | 15.3 | Add L   | inear Menu                    | 122 |

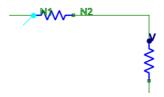

|    |      |         | Wire                          | 122 |

|    |      |         | Resistor, Inductor, Capacitor | 124 |

CONTENTS vii

|              | 15.3.3 Mutual Inductor          | 124 |

|--------------|---------------------------------|-----|

|              | 15.3.4 I/V sources and ground   | 124 |

|              | 15.3.5 Controlled sources       | 124 |

|              | 15.3.6 Switches                 | 124 |

|              | 15.3.7 Transmission lines       | 125 |

|              | 15.3.8 RC-Network               | 125 |

|              | 15.3.9 Subcircuit Pin           | 125 |

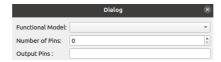

|              | 15.3.10 Functional model        | 125 |

|              | 15.3.11 Behavioural model       | 126 |

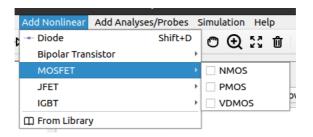

|              | 15.4 Add Nonlinear Menu         | 126 |

|              | 15.4.1 Nonlinear components     | 127 |

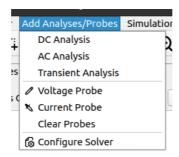

|              | 15.5 Add Analyses/Probes Menu   | 127 |

|              | 15.5.1 DC Analyses              | 128 |

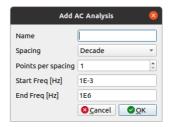

|              | 15.5.2 AC Analyses              | 128 |

|              | 15.5.3 Transient Analyses       | 128 |

|              | 15.5.4 Voltage/Current probes   | 129 |

|              | 15.5.5 Clear Probes             | 130 |

|              | 15.5.6 Configure Solver         | 130 |

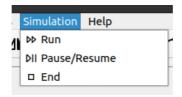

|              | 15.6 Simulation Menu            | 130 |

|              | 15.6.1 Run                      | 130 |

|              | 15.6.2 Pause/Resume             | 130 |

|              | 15.6.3 Stop                     | 130 |

|              | 15.7 Side-panes                 | 131 |

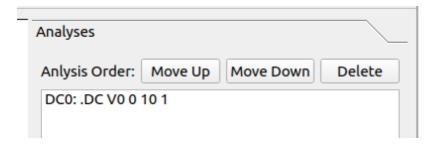

|              | 15.7.1 Analyses                 | 131 |

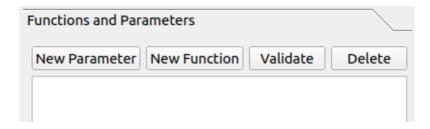

|              | 15.7.2 Functions and Parameters | 131 |

|              | 15.7.3 Components               | 132 |

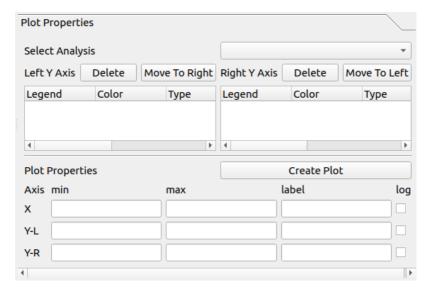

|              | 15.7.4 Plot Properties          | 132 |

|              | 15.7.5 Fitting/Optimization     | 132 |

| $\mathbf{A}$ | Notation and Acronyms           | 137 |

|              | Acronyms                        | 137 |

# Chapter 1

# Introduction

The circuit solver provided with the OESoft package performs various analyses of electronic circuit. It takes text files of circuit netlists in 'spice' format, and parses them to create a circuit matrix. The solver includes Newton's method based nonlinear solver for solving electronic circuits with nonlinear components. After a circuit is solved, all the solution quantities, i.e. all the node voltages and currents of each of the analysis (AC/DC/transient) are stored in a '.csv' file.

## 1.1 Features

The circuit solver has the following features.

- The circuit solver can perform a DC ramp, AC analysis at a fixed DC bias, and a transient analysis.

- A Newton's method based nonlinear solver is included. Since most of the electronic components exhibit nonlinear characteristics, a nonlinear solver is used in their circuit analyses.

- Parameters and functions can be defined and used in the main circuit or in a subcircuit. They are parsed using 'exprtk' parser.

- Values of various components can be parameterized, increasing reuse-ability of the circuit file.

## 1.2 Installation

OESoft currently supports software installation on various linux distributions. The software installer is available in debian package (\*.deb file) and in RPM format (\*.rpm file).

Note, that if you have downloaded mkl version of the Circuit Solver, the following package needs to be installed manually by you before installing the circuit solver from the installer package.

• Intel math kernel libraries (released in 2020 or later), which include distributions of open-mp, pardiso, etc. specific for intel processors.

The circuit solver sources mkl functions from the above installation. These functions can offer speed-up in the calculations on Intel processors. The mkl package can be downloaded from Intel website.

If the circuit solver without mkl acceleration is downloaded, then installation of the above package is not necessary.

Once Intel math kernel libraries are installed, download the installer on the local machine. The installer file named CircuitSolver\_amd64.deb will appear in the Downloads directory. Go to the directory using cd command. Use the following command to install the CircuitSolver from the installer.

```

>> sudo apt install ./CircuitSolver_amd64.deb

```

Alternately, one may use dpkg to install the software and use apt to install missing dependencies as follows.

```

>> sudo dpkg -i ./CircuitSolver_amd64.deb

>> sudo apt install -f

```

You need to have root access to install the software on your machine.

# 1.3 Licensing

Two types of licenses can be purchased for OESoft circuit solver.

- Node-locked license: Locked to the user's machine. The circuit solver software can run only on this machine. Both, unlimited and limited node-locked licenses of the circuit solver can be purchased from OESoft.

- Server license: A server running on one of the machines in the client organization. All the other machines contact the server to fetch the software licenses. The server license is locked to the specific machine in the client organization. Only limited server licenses of the circuit solver can be purchased.

Unlimited node-locked licenses enable unlimited number of simultaneous executions of the circuit solver on the client machine. With limited node-locked licenses, only the specified number of simultaneous executions of the circuit solver can be performed on the machine. The node-locked license limits the usage of the circuit solver only to the user's machine.

With *limited server licenses*, only the specified number of *simultaneous* executions of the circuit solver can be performed on all the machines in the client organization together. A server license enables usage of maximum the computational capability at the client organization.

# 1.3.1 Purchasing the licenses

The clients can place order on OES oft website or by contacting our sales-persons. Along with the name and the organization details, the clients need to provide -

- For the node-locked licenses: Ethernet mac address of the client machine on which the software will run.

OR

- For the server licenses: Ethernet mac address of the server machine at the client organization.

Ethernet mac address of the client machine can be obtained by running the following command on the client machine.

#### >> ifconfig eth0

The above command outputs various eth0 config settings. Search for the keyword ether and write down the mac-id following ether. The mac-id mush have the following format – xx:xx:xx:xx:xx;xx, where x stands for a number (0-9) or a letter (a-f). You need to send this mac id to us to receive the licenses. The same procedure can be followed on the server machine to receive its mac-id.

Sometimes, >> ifconfig eth0 does not give any output. In that case, please run the following command.

#### >> ifconfig -a

Search for the interface which begins with enp or eno. Kindly provide mac address of that interface. If interfaces which begin with both enp and eno are present, priority is given to enp.

We will process the request and send the license files on a secured email. The license files need to be activated on the same machines using the license key which is emailed separately. The activation procedure is described below.

#### 1.3.2 Node-locked license activation

If you purchased one or more node-locked licenses, you will receive the following license file by secured email.

NodeLockedLicense\_<id>>\_<Info>.lic, where <id>> stands for license id and <Info> stands for customer identification in short.

Execute the following commands with admin access rights—

- >> sudo cp NodeLockedLicense\*.lic \

/var/local/oesoft/licenses/ONodeLockedLicense.lic

- >> sudo chmod 666 /var/local/oesoft/licenses/ONodeLockedLicense.lic

Any additional node-locked license purchased from us can be activated in the same way as above. Every additional activated license file can be stored at /var/local/oesoft/licenses by the name i>00,1,2,...49). The circuit solver will read the license files and lock the first available license.

1.3. LICENSING 5

#### 1.3.3 Server license activation

If you purchased one or more server licenses, you will receive the following license files by secured email.

#### 1. ServerLicense <id> <Info>.lic

Copy the above files to the server machine and execute the following commands with admin access rights—

```

>> sudo cp ServerLicense*.lic \

/usr/share/oesoft/licenses/0ServerLicense.lic

```

Do not forget to add the following line to .bashrc file of each of the users.

```

export OESOFT_LICENSE_SERVER='<port>@<server>'

```

Any additional server license purchased from us can be stored in the same way as above. Every additional activated license file can be stored at /usr/share/oesoft/licenses by the name <i>ActiveLicense.lic, where i = (0, 1, 2, ...49). The circuit solver will read the license files and lock the first available license.

### 1.3.4 Testing

User-guides of all the software provided by OESoft are stored at the location /opt/oesoft/userguides/.

Tutorials of all the software provided by OESoft are stored at the location /opt/oesoft/tutorials/.

Copy any one of the tutorial directory from /opt/oesoft/tutorials/CircuitSol to your working directory and run the spice circuit file in it using the following command.

#### >> CircuitSolver <filename>.cir

If licenses are activated, then the above command should not give any license error.

# Chapter 2

# Linear Components

Linear components can be separated into passive components, active components, and dependent sources. They are described below.

# 2.1 Passive Components

#### 2.1.1 Resistor

A new line starting with the letter R defines a resistor. The first string is the component name and the next two strings are names of the nodes connected by the resistor. For example, a resistor of value r Ohms is instantiated between the nodes n1 and n2 by the following line.

It connects voltages between the two nodes by the following relationship.

$$V(n2) - V(n1) = I_{n1 \to n2} \cdot r \tag{2.1}$$

where  $I_{n1\to n2}$  is DC/AC/transient current flowing from node n1 to n2, V(n1) and V(n2) are DC/AC/transient voltages at n1 and n2.

Temperature response of the resistor can be defined using the following equation.

$$R(T) = R + CT1 \cdot (T - Tnom) + CT2 \cdot (T - Tnom)^2 \tag{2.2}$$

The parameters CT1, CT2, and TEMP can be defined together with the resistor definition as follows.

#### 2.1.2 Inductor

A new line starting with the letter L defines an inductor. The first string is the component name and the next two strings are names of the nodes connected by the inductor. For example, an inductor of value l Henri is instantiated between the nodes n1 and n2 by the following line.

In AC analysis, the inductor connects voltages between the two nodes by the following relationship.

$$V(n2) - V(n1) = I_{n1 \to n2} \cdot j\omega l \tag{2.3}$$

where  $I_{n1\to n2}$  is phasor current flowing from node n1 to n2, V(n1) and V(n2) are phasor voltages at n1 and n2.

In transient analysis, the inductor connects voltages between the two nodes by the following relationship.

$$V(n2) - V(n1) = l \cdot \frac{dI_{n1 \to n2}}{dt}$$

(2.4)

where  $I_{n_1 \to n_2}$  is transient current flowing from node  $n_1$  to  $n_2$ ,  $V(n_1)$  and  $V(n_2)$  are phasor voltages at  $n_1$  and  $n_2$ .

In DC analysis, the inductor is replaced by a 1nOhm resistance.

#### 2.1.3 Mutual inductance

Each new line starting with the letter K creates a mutual inductance between the inductances whose names are listed after the first word. First word after the inductor names is regarded as a mutual coupling coefficient m < 1.0. More that two inductors can be listed as coupled inductances. In this case, the coupling coefficient between each pair of inductances is set to m.

If mutual inductance between any two inductors is defined on multiple lines, the previously defined values are overwritten by the latest value.

Mutual inductance can be used to model a transformer, or an electric motor, etc.

## 2.1.4 Capacitor

A new line starting with the letter  ${\tt C}$  defines a capacitor. The first string is the component name and the next two strings are names of the nodes connected by the capacitor. For example, a capacitor of value c Henri is instantiated between the nodes n1 and n2 by the following line.

In AC analysis, the capacitor connects voltages between the two nodes by the following relationship.

$$V(n2) - V(n1) = I_{n1 \to n2} \cdot \frac{1}{j\omega c}$$

(2.5)

where  $I_{n1\to n2}$  is phasor current flowing from node n1 to n2, V(n1) and V(n2) are phasor voltages at n1 and n2.

In transient analysis, the capacitor connects voltages between the two nodes by the following relationship.

$$I_{n1\to n2} = c \cdot \frac{d(V(n2) - V(n1))}{dt}$$

(2.6)

where  $I_{n1\to n2}$  is transient current flowing from node n1 to n2, V(n1) and V(n2) are phasor voltages at n1 and n2.

In DC analysis, the capacitor is replaced by a  $10^20$  Ohm resistance.

# 2.2 Active components

## 2.2.1 Voltage source

A new line starting with the letter V defines a voltage source. The first string is the component name and the next two strings are names

of the nodes connected by the voltage source. The strings after than define the AC, DC, and transient voltage. For example, a voltage source is instantiated between the nodes n1 (positive node) and n2 by the following line.

Vinput n1 n2 DC 0.0 AC 1.0 90 SIN(0.8 0.025 100.)

The number after DC sets DC voltage which is used in DC analysis. The two numbers after AC set phasor voltage and phase (in degrees) of the voltage source, which is used in AC analysis. The string after that specifies the type of the transient waveform together with the parameters in parentheses (...).

#### 2.2.2 Current source

A new line starting with the letter I defines a current source. The first string is the component name and the next two strings are names of the nodes connected by the voltage. The strings after than define the AC, DC, and transient voltage. For example, a current source is instantiated from node n1 to n2 by the following line.

Iinput n1 n2 DC 0.0 AC 1.0 90 SIN(0.8 0.025 100.)

The number after DC sets DC current which is used in DC analysis. The two numbers after AC set phasor current and phase (in degrees) of the current source, which is used in AC analysis. The string after that specifies the type of the transient waveform together with the parameters in parentheses (...).

## 2.2.3 Transient waveform shapes

Following transient waveform types are supported.

- SIN(p1 p2 p3 ...) Sinusoidal pulse is used. Parameters listed in the parentheses have the following meaning.

- 1. p1 DC bias (Volts),

- 2. p2 AC peak voltage (Volts),

- 3. p3 frequency (Hertz),

- 4. p4 time delay (sec),

- 5. p5 exponential decay factor in the prefactor (1/sec),

- 6. p6 initial phase (degrees),

- PWL(...) Piece-wise linear waveform. List of time and voltage at that time are specified in parantheses. For example, PWL(0. 0. 1. 1. 2. 1. 3. 0.) specifies voltage waveform which where V(0) = 0, V(1) = 1, V(2) = 1, and V(3) = 0.

- PULSE(...) Rectangular pulse is used. Parameters listed in the parantheses have the following meaning.

- 1. p1 voltage at logical zero,

- 2. p2 voltage at logical one,

- 3. p3 delay time,

- 4. p4 rise time,

- 5. p5 fall time,

- 6. p6 pulse width of logical one,

- 7. p6 pulse period.

# 2.3 Dependent sources

#### 2.3.1 Voltage-controlled voltage source

A new line starting with the letter E defines a Voltage-controlled Voltage Source (VCVS). The first string is the component name. The next two strings are names of the positive and negative nodes of controlled-voltage source. The next two strings are the names of positive and negative controlling voltage sources in the VCVS. For example, a VCVS of voltage gain v between the nodes N+ and N- with the controlling source between NC+ and NC- is instantiated by the following line.

It connects voltages between the four nodes by the following relationship.

$$V(N+) - V(N-) = v \cdot [V(NC+) - V(NC-)]$$

(2.7)

where V(N+), V(N-), V(NC+), and V(NC-) are DC/AC/transient voltages at respective nodes.

#### Nonlinear VCVS

A VCVS with nonlinear dependence on the input voltage is defined by specifying higher degree polynomial coefficients as follows.

The resulting components links voltages between the four nodes as follows.

$$V_{in} = [V(NC+) - V(NC-)] V(N+) - V(N-) = v1 \cdot V_{in} + v2 \cdot V_{in}^2 + v3 \cdot V_{in}^3 + (2.8)$$

The nonlinear VCVS is solved by the nonlinear circuit solver using Newton's method.

## 2.3.2 Voltage-controlled Current source

A new line starting with the letter  ${\tt G}$  defines a Voltage-controlled Current Source (VCCS). The first string is the component name. The next two strings are names of the nodes of the controlled-current source. The next two strings are the names of positive and negative controlling voltage sources in the VCCS. For example, a VCCS of transconductance g between the nodes N+ and N- with the controlling source between NC+ and NC- is instantiated by the following line.

It connects voltages between the four nodes by the following relationship.

$$I_{N+\to N-} = v \cdot [V(NC+) - V(NC-)]$$

(2.9)

where  $I_{N+\to N-}$  is the current from N+ to N-, while V(NC+), and V(NC-) are DC/AC/transient voltages at respective nodes.

#### Nonlinear VCCS

A VCCS with nonlinear dependence on the input voltage is defined by specifying higher degree polynomial coefficients as follows.

The resulting components links voltages between the four nodes as follows.

$$V_{in} = [V(NC+) - V(NC-)] I_{N+\to N-} = g1 \cdot V_{in} + g2 \cdot V_{in}^2 + g3 \cdot V_{in}^3 + \cdots$$

(2.10)

The nonlinear VCCS is solved by the nonlinear circuit solver using Newton's method.

#### 2.3.3 Current-controlled voltage source

A new line starting with the letter H defines a Current-controlled Voltage Source (CCVS). The first string is the component name. The next two strings are names of the positive and negative nodes of controlled-voltage source. The next string is name of the voltage source from which the current is measured. For example, a CCVS of trans-resistance h between the nodes N+ and N- with Vname is voltage source name through which controlling current is measured is instantiated by the following line.

#### Hc N+ N- Vname h

It connects voltages between the four nodes by the following relationship.

$$V(N+) - V(N-) = h \cdot [I(Vname)]$$

(2.11)

where V(N+) and V(N-) are DC/AC/transient voltages at respective nodes and I(Vname) is current through the voltage source Vname.

#### Nonlinear CCVS

A CCVS with nonlinear dependence on the input current is defined by specifying higher degree polynomial coefficients as follows.

Hc N+ N- Vname h1 h2 h3 ...

The resulting components links voltages between the four nodes as follows.

$$V(N+) - V(N-) = h1 \cdot I(\text{Vname}) + h2 \cdot I(\text{Vname})^2 + h3 \cdot I(\text{Vname})^3 + \cdots$$

(2.12)

The nonlinear CCVS is solved by the nonlinear circuit solver using Newton's method.

#### 2.3.4 Current-controlled current source

A new line starting with the letter F defines a Current-controlled Current Source (CCCS). The first string is the component name. The next two strings are names of the nodes of controlled current source. The next string is name of the voltage source from which the controlling current is measured.

For example, a CCCS of trans-resistance f between the nodes N+ and N- with Vname as voltage source name through which controlling current is measured is instantiated by the following line.

Fc N+ N- Vname f

It connects voltages between the four nodes by the following relationship.

$$I_{N+\to N-} = h \cdot [I(\text{Vname})]$$

(2.13)

where  $I_{N+\to N-}$  is the current from N+ to N- while I(Vname) is current through voltage source with name Vname.

#### Nonlinear CCCS

A CCCS with nonlinear dependence on the input current is defined by specifying higher degree polynomial coefficients as follows.

Fc N+ N- Vname f1 f2 f3 ...

2.4. SWITCHES 15

The resulting components links voltages between the four nodes as follows.

$$I_{N+\to N-} = f1 \cdot I(\text{Vname}) + f2 \cdot I(\text{Vname})^2 + f3 \cdot I(\text{Vname})^3 + \cdots$$

(2.14)

The nonlinear CCVS is solved by the nonlinear circuit solver using Newton's method.

#### 2.4 Switches

## 2.4.1 Voltage-controlled switch

A new line starting with the letter S defines a switch. The first string is the component name. The next two strings are names of the nodes between which the switch is connected. The next two strings are the names of positive and negative controlling voltage sources in the switch. For example, a switch between the nodes N+ and N- with the controlling source between NC+ and NC- is instantiated by the following line.

```

.model Sw Switch(ROFF=1E12 RON=1E-2 VT=0.5 VH=0)

Sb N+ N- NC+ NC- Sw

```

When the switch is off, a resistor of resistance ROFF is connected between the nodes, N+ and N-. In the on-state of the, the switch resistance takes the value of RON.

The switch has three modes of operation depending on VH.

If VH is zero, switching happens when difference Vin = V(NC+) - V(NC-) is equal to VT.

If VH is positive, the switch shows hysteresis. That is, the switch turns on when Vin rises above VT + VH, and turns off when Vin falls below VT - VH.

If VH is negative, the switch resistance smoothly transitions between RON and ROFF. The transition occurs between Vin of VT + VH and VT - VH. The transition follows a linear fit to the logarithm of the switch's conduction.

#### 2.4.2 Current-controlled switch

A new line starting with the letter  $\mathbb W$  defines a switch. The first string is the component name. The next two strings are names of the nodes between which the switch is connected. The next string is name of the voltage source from which the controlling current is measured. For example, a switch between the nodes N+ and N- with Vname as voltage source name through which controlling current is measured, is instantiated by the following line.

```

.model Sw Switch(ROFF=1E12 RON=1E-2 IT=0.5 IH=0)

Wb N+ N- Vname Sw

```

When the switch is off, a resistor of resistance ROFF is connected between the nodes, N+ and N-. In the on-state of the, the switch resistance takes the value of RON.

The switch has three modes of operation depending on IH.

If IH is zero, switching happens when difference I(Vname) is equal to IT.

If IH is positive, the switch shows hysteresis. That is, the switch turns on when I(Vname) rises above IT + IH, and turns off when I(Vname) falls below IT - IH.

If IH is negative, the switch resistance smoothly transitions between RON and ROFF. The transition occurs between I(Vname) of IT + IH and IT - IH. The transition follows a linear fit to the logarithm of the switch's conduction.

## 2.5 Transmission line models

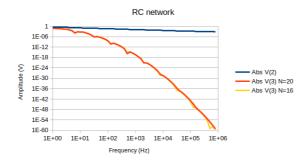

#### 2.5.1 RC Network

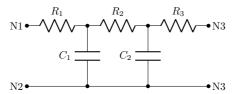

A new line starting with the letter U defines a 4-terminal component which models a RC network as a lumped model consisting of user-specified number of RC segments. The first string is the component name. The next three strings are names of the nodes on the left and the right side of the TL (see Fig. 2.2). The next string specifies the RC model.

Figure 2.1: Equivalent circuit of the RC-network component having two RC-segments. Note, there are always N+1 resistors and N capacitors in the network.

For example, a RC network between the nodes N1, N2, and N3 is instantiated by the following line.

.model RC1 TL (N=2 R=1 C=1)

Uname N1 N2 N3 RC1

Note, that for a given N segment RC network, there are always N+1 resistors and N capacitors in the network, to make it symmetric with respect to nodes N1 and N2.

Lengths of RC segments in the network are in geometric progression, with longest segment being at the center and shortest segments at the N1 and N2 ends. K is set as the constant of geometric progression. With this arrangement, frequency response of the network remains the same independent of N, for a *sufficiently* large value of N.

All the input parameters of the RC network are listed in Table 2.1. If ISPERL is greater than zero, then capacitors in the RC network are modeled as diodes with depletion capacitance of CPERL per meter and leakage current of ISPERL per meter. The diodes are connected such that anodes of all the diodes are connected to N3.

**Note:** For a RC network, number of lumped RC-segments must be specified while defining the component. They cannot be changed afterwards.

| Parameter | Description                                   | Default | Unit       |

|-----------|-----------------------------------------------|---------|------------|

| N         | Number of lumped RC-segments                  | 6       | -          |

| RPERL     | Resistance per meter                          | 1       | $\Omega/m$ |

| CPERL     | Capacitance per meter                         | 1       | F/m        |

| L         | Length of the RC network                      | 1       | meter      |

| K         | Propagation Constant                          | 2       | -          |

| FMAX      | Maximum Frequency of interest                 | 1G      | $_{ m Hz}$ |

| TC1       | Linear temperature coefficient of resistor    | 0       | -          |

| TC2       | Quadratic temperature coefficient of resistor | 0       | -          |

| TEMP      | Temperature                                   | 300     | K          |

| ISPERL    | Diode leakage current per meter               | 0       | A/m        |

Table 2.1: Input parameters of the RC network

#### 2.5.2 Lossless TL

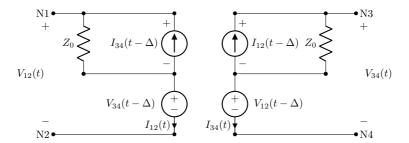

A new line starting with the letter T defines a 4-terminal component which mimics a *lossless* TL as a distributed network. The first string is the component name. The next four strings are names of the nodes on the left and the right side of the TL (see Fig. 2.2). The next string specifies the TL model.

For example, a TL between the nodes N1, N2, N3, and N4 is instantiated by the following line.

```

.model Tl1 TL (Z0=1 TD=1)

.model Tl2 TL (Z0=1 F=1 NL=1)

Tname N1 N2 N3 N4 Tl1

```

Input parameters of the lossless TL component are listed in Table 2.2. Either the parameter TD must be specified or F and ND must be specified. If F and ND are set, then TD is calculated as  $\frac{NL}{F}$ .

Implementation of the distributed TL model is shown in Fig. 2.2.

| Table 2.2: Input parameters of the lossless TL |                                 |         |                       |  |

|------------------------------------------------|---------------------------------|---------|-----------------------|--|

| Parameter                                      | Description                     | Default | $\operatorname{Unit}$ |  |

| ZO                                             | input impedence = $\frac{L}{C}$ | 1       | Ω                     |  |

| TD                                             | delay                           | 0       | sec                   |  |

| F                                              | frequency                       | 1       | $_{ m Hz}$            |  |

| ND                                             | normalized length of TL         | 0       | _                     |  |

Figure 2.2: Equivalent circuit of the lossless transmission line. The parameters, input impendence (Z0) and delay ( $\Delta$ ) are specified by the user.

| Table 2.5. Input parameters of the lossy 1L |                       |         |            |  |

|---------------------------------------------|-----------------------|---------|------------|--|

| Parameter                                   | Description           | Default | Unit       |  |

| L                                           | Inductance per meter  | 1       | H/m        |  |

| С                                           | Capacitance per meter | 1       | F/m        |  |

| R                                           | Resistance per meter  | 1       | $\Omega/m$ |  |

| LEN                                         | Length of TL          | 0       | meter      |  |

Table 2.3: Input parameters of the lossy TL

## 2.5.3 Lossy Transmission line

A new line starting with the letter 0 defines a 4-terminal component which models a *lossy* TL as a distributed network. The first string is the component name. The next four strings are names of the nodes on the left and the right side of the TL. The next string specifies the TL model.

For example, a TL between the nodes N1, N2, N3, and N4 is instantiated by the following line.

.model Tl1 TL (L=1 C=1 R=1 LEN=1)

Oname N1 N2 N3 N4 Tl1

Input parameters of the lossy TL are listed in Table 2.3.

**Note:** Alternating Current (AC) response of lossy TL component is not modeled. In AC analysis, a lossy TL is treated as a lossless TL.

# Chapter 3

# Transfer-function or state-space models

Frequency response of a linear time invariant (LTI) system is given by the transfer-function. Modeling the temporal response of the system requires state-space representation of the system. This chapter describes modeling of such a system when transfer-function or state-space representation of the system is known.

## 3.1 Transfer-function model

A LTI system which takes a time-varying scalar signal x(t) as input and outputs time-varying signal y(t), is modeled by the transfer function as follows,

$$H(s) = \frac{Y(s)}{X(s)}$$

$$= \frac{n_0 + n_1 \cdot s + n_2 \cdot s^2 + \cdots}{m_0 + m_1 \cdot s + m_2 \cdot s^2 + \cdots}$$

$$= \frac{\sum_{0}^{N} n_i \cdot s^i}{\sum_{0}^{M} m_i \cdot s^i}$$

(3.1)

Here,  $m_i$ ,  $n_i$  are real numbers and  $s = j\omega = j2\pi f$  is frequency of the input signal. M and N are positive integers, with M is the order of the system.

# 3.2 State-space model

Any generic LTI system with time-varying input (x(t)) and time-varying output (y(t)), is modeled by the following set of differential equations.

$$\begin{aligned}

\dot{q_1} &= a_{1,1}q_1 + \dots + a_{1,M}q_M + b_1x(t) \\

\dots \\

\dot{q_i} &= a_{i,1}q_1 + \dots + a_{i,M}q_M + b_ix(t) \\

\dots \\

\dot{q_M} &= a_{M,1}q_1 + \dots + a_{M,M}q_M + b_Mx(t) \\

y(t) &= c_1q_1 + \dots + c_Mq_M + D \cdot x(t)

\end{aligned} (3.2)$$

In the above,  $a_{i,i}, b_i, c_i$ , and D are real numbers,  $\dot{q}_i = \frac{dq_i}{dt}$  represents time derivative of state variable q(t).

The above set of differential equations can be written in matrix notation as follows.

$$\frac{d\vec{q}}{dt} = \dot{\vec{q}} = A_{M \times M} \cdot \vec{q} + B_{M \times 1} \cdot x(t) \tag{3.3}$$

$$y(t) = C_{1 \times M} \cdot \vec{q} + D \cdot x(t) \tag{3.4}$$

Here, M is system order, A is a  $M \times M$  square matrix, B and C are vectors of length M, and D is a scalar.  $\vec{q}$  is a vector of length M of state-variables of the system.

**Note:** The transfer-function model described in Sec. 3.1 and state-space model described in Sec. 3.2 are two ways of describing the same LTI system. That is, specifying the system with any one of the these two models is sufficient.

# 3.3 Circuit model of the system

The LTI system described above is modeled in the circuitsolver by controlled sources. The voltage/current at the controlling source acts

as an input signal (x(t)) whereas the output signal y(t) is the output V/I source.

Thus, if the LTI system is modeled as a VCVS (see Chapter 3, Sec. 2.3.1), input signal x(t) is the voltage difference between input pins N3 and N4, while signal y(t) is a time-varying voltage source between output pins N1 and N2.

For a VCCS, input signal x(t) is the voltage difference between input pins N3 and N4, while signal y(t) is a time-varying *current* source connected between output pins N1 and N2.

For a CCVS, input signal x(t) is the current through the controlling voltage source, while signal y(t) is a time-varying *voltage* source connected between output pins N1 and N2.

For a CCCS, input signal x(t) is the current through the controlling voltage source, while signal y(t) is a time-varying *current* source connected between output pins N1 and N2.

#### 3.3.1 Transfer-function definition

A VCVS system, whose response is given by the transfer-function given by Eq. 3.5,

$$H(s) = \frac{Y(s)}{Xs} = \frac{n_0 + n_1 \cdot s + n_2 \cdot s^2}{m_0 + m_1 \cdot s + m_2 \cdot s^2 + m_3 \cdot s^3}$$

(3.5)

can be specified as follows.

Eb N1 N2 N3 N4 TransFunc Mmat=(m0 m1 m2 m3) Nmat=(n0 n1 n2)

The above line defines a VCVS component which links voltages between the four nodes by the transfer function, such that V(N1) - V(N2) = y(t) and V(N3) - V(N4) = x(t). The keyword TransFunc denotes that transfer-function of the system is provided. Note, that order of the system is defined by the number of entries in Mmat. Number of entries in Nmat is less than that in Mmat. Unspecified higher order entries of Nmat are set to 0.

#### 3.3.2 State-space definition

If, instead of the transfer-function, state-space model of the VCVS system is known and given by Eq. 3.6.

$$\begin{aligned}

\dot{q}_1 &= a_{1,1}q_1 + a_{1,2}q_2 + b_1x(t) \\

\dot{q}_2 &= a_{2,1}q_1 + a_{2,2}q_2 + b_2x(t) \\

y(t) &= c_1q_1 + c_2q_2 + D \cdot x(t)

\end{aligned} (3.6)$$

The VCVS system can be modeled by the following line.

Eb N1 N2 N3 N4 StateSpace Amat=(a11 a12 a21 a22) Bmat=(b1 b2) Cmat=(

The keyword, StateSpace denotes that state-space model of the system is provided. Notice, that parameter names Amat lists entries of matrix A in *row major* format. The parameter names Bmat and Cmat list entries of the respective vectors, while D lists the scalar.

Entry at a specific row and column in the matrix/vector can be specified by using the parameter name in the following format-<Matrix>\_r\_c. For example, to set entry in the 2nd row, 1st column of A matrix, specify it with the parameter name A\_2\_1. Notice the use of A instead of Amat as prefix. Also, notice that row and column ids start from one (instead of zero). Entry a21 of matrix A will be overwritten by the value of the parameter A\_2\_1. The parameter A\_2\_1 can take parametric entries as well. For example, if par1 is defined in the subcircuit, then A\_2\_1={par1} is a valid assignment.

# Chapter 4

# Non-linear Components

Circuits with nonlinear components (e.g. diodes) cannot be solved by a direction matrix equation  $(A \cdot x = b)$  solver. In the case of nonlinear devices, the circuit matrix is a function of the solution variable (i.e.  $A(x) \cdot x = b(x)$ ). Such a system needs to be solved by a nonlinear solver method such as 'Newton method'.

The circuit solver employs a damped Newton's method proposed by Bank-Rose in solving the nonlinear equation. For that purpose, derivatives of the node equation w.r.t. solution variables are calculated and used in the circuit matrix. Available nonlinear components are described below together with the node equations corresponding to each of the nonlinear component.

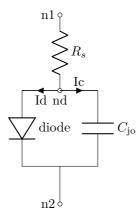

# 4.1 Diode component

A new line starting with the letter D defines a diode. The first string is the component name and the next two strings are names of node connected to the anode and cathode. The next string is the name of the diode model. The next three numbers are, respectively, diode area, initial DC voltage, and junction temperature.

For example, a diode of area scaling factor a is instantiated between anode N+ and cathode N- by the following lines. Note, that the model 'Da1N4004' with various hyper-parameters of the diode is also

Figure 4.1: Equivalent circuit of the diode component

written.

```

.model Da1N4004 D ( IS=18.8n RS=0 BV=400 IBV=5.00u + CJ0=1.E-9 M=0.333 N=2 TT=1E-6)

Di N+ N- Da1N4004 a

```

A resistor in series with and a capacitor in parallel to the 'ideal' diode are present in the above model. Together with them, equivalent circuit of the diode is shown in Fig. 4.1.

Parameters accepted by the 'diode' component are listed in Table 4.1 together with their meaning, default value, and the unit.

The following equations are solved in the 'ideal' diode.

$$I_{n1 \to n2} = Id + Ic \tag{4.1}$$

$$Vd = V(ns) - V(n2) \tag{4.2}$$

$$V(n1) - V(n2) = RS \cdot (Id + Ic) + Vd \tag{4.3}$$

$$Id = area \cdot (I_{\text{fwd}} - I_{\text{rev}}) \tag{4.4}$$

$$I_{\text{fwd}} = IS \cdot \left( \exp\left(\frac{Vd}{\eta V_T}\right) - 1 \right) + G_{min} \cdot (Vd)$$

(4.5)

Table 4.1: Input parameters of the diode component

| Parameter | Description                                       |            | Unit             |

|-----------|---------------------------------------------------|------------|------------------|

| IS        | saturation current                                | $10^{-14}$ | $A/m^2$          |

| RS        | series resistance                                 | 0          | Ω                |

| N         | emission coefficient                              | 1          | -                |

| BV        | breakdown voltage                                 | $10^{10}$  | V                |

| IBV       | current at breakdown voltage                      | $10^{-5}$  | $A/m^2$ $F/m^2$  |

| CJO       | zero-bias junction capacitance                    | 0          | $F/m^2$          |

| VJ        | junction potential                                | 0.8        | V                |

| M         | grading coefficient                               | 0.5        | -                |

| TT        | transit time                                      | 0          | sec              |

| FC        | coefficient in forward-bias depletion capacitance | 0.5        | -                |

| EG        | band-gap of the diode material                    | 1.1        | eV               |

| TEMP      | junction temperature                              | 300.       | K                |

| XTI       | IS temperature exponent                           | 3.0        | -                |

| TBV1      | BV temperature coefficient (linear)               | 0          | 1/K              |

| TBV2      | BV temperature coefficient (quadratic)            | 0          | $1/\mathrm{K}^2$ |

| TRS1      | RS temperature coefficient (linear)               | 0          | 1/K              |

| TRS2      | RS temperature coefficient (quadratic)            | 0          | $1/K^2$          |

$$I_{\text{rev}} = IBV \cdot \left( \exp\left(\frac{-(Vd + BV)}{\eta V_T}\right) - 1 \right) - \frac{BV}{V_T}$$

(4.6)

Junction capacitance parallel to the diode is modeled as follows.

$$C_{\text{io}} = area \cdot (Cd + Cj) \tag{4.7}$$

$$Cj = CJO \cdot \left(1 - \frac{Vd}{VJ}\right)^{-M} \tag{4.8}$$

$$Cd = TT \cdot \frac{IS}{nV_T} \cdot \exp\left(\frac{Vd}{nV_T}\right) \tag{4.9}$$

where  $I_{n1\to n2}$  is DC/AC/transient current flowing from node n1 to n2, V(n1) and V(n2) are DC/AC/transient voltages at n1 and n2. For convergence purpose, a resistor with the resistance of  $1/G_{min}$  is connected in parallel with the diode.

Diode characteristics are temperature dependent. Temperature dependence if IS, BV, and RS is modeled using the following equations.

$$IS(T) = IS \cdot \exp\left(\left(\frac{T}{TNOM} - 1\right) \frac{EG}{N \cdot \phi_T}\right) \cdot \left(\frac{T}{TNOM}\right)^{XTI/N} \tag{4.10}$$

$$BV(T) = BV + TBV1 \cdot (T - TNOM) + TBV1 \cdot (T - TNOM)^{2}$$

$$(4.11)$$

$$RS(T) = RS + TRS1 \cdot (T - TNOM) + TRS1 \cdot (T - TNOM)^{2}$$

$$(4.12)$$

(4.13)

Temperature of the diode can be set by the parameter TEMP. If this parameter is not explicitly set, temperature dependence is disabled.

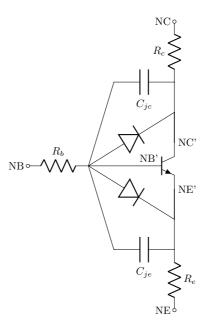

# 4.2 BJT component

A new line starting with the letter Q defines a Bipolar Junction Transistor (BJT). The first string is the component name and the next three strings are names of the nodes connected to the collector, base, and emitter of the BJT. The next string is the name of the BJT model. The next number is the BJT area factor.

Figure 4.2: Equivalent circuit of the BJT component

For example, a BJT of area scaling factor a is instantiated with collector NC, base NB, and emitter NE in the following lines. Note, that the model '2N2222' of an npn BJT with various hyper-parameters is also written.

# .model 2N2222 NPN (ISE=1E-14 ISC=1E-14 BF=100 BR=3) Q1 NC NB NE 2N2222 a

Resistors RC, RB, and RE are added in series with each of the collector, base, and emitter, respectively. Junction capacitors CJC and CJE are added in parallel to the 'ideal' diodes present at base-collector and base-emitter junctions, respectively. Together with them, equivalent circuit of the BJT is shown in Fig. 4.2.

Parameters accepted by the 'BJT' component are listed in Table 4.2 together with their meaning, default value, and the unit.

The ideal BJT in Fig. 4.2 is modeled by the Ebers-Mol equations given below.

$$I_{NB' \to NE'} = area \cdot IS \cdot \left( \exp\left(\frac{V(NB) - V(NE)}{\eta_F V_T}\right) - 1 \right) - \alpha_R \cdot I_{NB' \to NC'}$$

$$(4.14a)$$

$$I_{NB' \to NC'} = area \cdot IS \cdot \left( \exp\left(\frac{V(NB) - V(NC)}{\eta_F V_T}\right) - 1 \right) - \alpha_F \cdot I_{NB' \to NE'}$$

$$I_{NB'\to NC'} = area \cdot IS \cdot \left(\exp\left(\frac{V(NB) - V(NC)}{\eta_R V_T}\right) - 1\right) - \alpha_F \cdot I_{NB'\to NE'}$$

(4.14b)

Note, that the above equations are valid for 'NPN' BJT. For a PNP BJT, the following equations are solved.

$$I_{NE' \to NB'} = area \cdot IS \cdot \left( \exp\left(\frac{V(NE) - V(NB)}{\eta_F V_T}\right) - 1 \right) - \alpha_{\rm R} \cdot I_{NC' \to NB'}$$

$$(4.15a)$$

$$I_{NC' \to NB'} = area \cdot IS \cdot \left( \exp\left(\frac{V(NC) - V(NB)}{\eta_R V_T}\right) - 1 \right) - \alpha_F \cdot I_{NE' \to NB'}$$

$$(4.15b)$$

Ideal diodes in Fig. 4.2 represent leakage current at B-C and B-E junctions. This leakage current does not take part in BJT action. Currents through these diodes are modeled by the following equations.

$$Vbe = V(NB') - V(NE') \tag{4.16}$$

$$I_{\text{de}} = area \cdot ISE \cdot \left( \exp\left(\frac{Vbe}{\eta_E V_T}\right) - 1 \right) + G_{min} \cdot (Vbe)$$

(4.17)

$$Vbc = V(NB') - V(NC') \tag{4.18}$$

$$I_{\rm dc} = area \cdot ISC \cdot \left( \exp\left(\frac{Vbc}{\eta_C V_T}\right) - 1 \right) + G_{min} \cdot (Vbc) \tag{4.19}$$

Note, that the above equations are valid for 'NPN' BJT. Polarities of the diodes are reverse in a 'PNP' BJT.

Table 4.2: Input parameters of the BJT component

| Parameter | Description                                       | Default    | Unit             |

|-----------|---------------------------------------------------|------------|------------------|

| IS        | transport saturation current                      | $10^{-14}$ | $A/m^2$          |

| ISE       | B-E leakage saturation current                    | 0          | $A/m^2$          |

| ISC       | B-C leakage saturation current                    | 0          | $A/m^2$          |

| BF        | ideal forward beta                                | 100        | A                |

| BR        | ideal reverse beta                                | 100        | A                |

| NF        | forward emission coefficient                      | 1          | A                |

| NR        | reverse emission coefficient                      | 1          | A                |

| RE        | emitter series resistance                         | 0          | Ω                |

| RC        | collector series resistance                       | 0          | Ω                |

| RB        | base series resistance                            | 0          | Ω                |

| NE        | B-E leakage emission coefficient                  | 1.5        | -                |

| NC        | B-C leakage emission coefficient                  | 1.5        | -                |

| VJE       | B-E junction potential                            | 0.8        | V                |

| VJC       | B-C junction potential                            | 0.8        | V                |

| CJE       | B-E zero-bias depletion capacitance               | 0          | $F/m^2$          |

| CJC       | B-C zero-bias depletion capacitance               | 0          | $F/m^2$          |

| TF        | forward transit time                              | 0          | sec              |

| TR        | reverse transit time                              | 0          | sec              |

| MJE       | B-E junction grading coeff.                       | 0.5        | -                |

| MJC       | B-C junction grading coeff.                       | 0.5        | -                |

| FC        | coefficient in forward-bias depletion capacitance | 0.5        | -                |

| EG        | band-gap of the diode material                    | 1.1        | eV               |

| TEMP      | junction temperature                              | 300.       | K                |

| XTI       | ISE and ISC temperature exponent                  | 3.0        | -                |

| XTB       | BF and BR temperature exponent                    | 0          | -                |

| TRE1      | RE temperature coefficient (linear)               | 0          | 1/K              |

| TRE2      | RE temperature coefficient (quadratic)            | 0          | $1/\mathrm{K}^2$ |

| TRB1      | RB temperature coefficient (linear)               | 0          | 1/K              |

| TRB2      | RB temperature coefficient (quadratic)            | 0          | $1/\mathrm{K}^2$ |

| TRC1      | RE temperature coefficient (linear)               | 0          | 1/K              |

| TRC2      | RE temperature coefficient (quadratic)            | 0          | $1/\mathrm{K}^2$ |

The semiconductor junction capacitances  $C_{je}$  and  $C_{jc}$  are modeled as follows.

$$C_{je} = area \cdot (Cde + Cje') \tag{4.20}$$

$$Cje' = CJE \cdot \left(1 - \frac{Vd}{VJE}\right)^{-MJE} \tag{4.21}$$

$$Cde = TF \cdot \frac{ISE}{\eta_E V_T} \cdot \exp\left(\frac{Vd}{\eta_E V_T}\right)$$

(4.22)

$$C_{\rm ic} = area \cdot (Cdc + Cjc') \tag{4.23}$$

$$Cjc' = CJC \cdot \left(1 - \frac{Vd}{VJC}\right)^{-MJC} \tag{4.24}$$

$$Cdc = TF \cdot \frac{ISC}{\eta_C V_T} \cdot \exp\left(\frac{Vd}{\eta_C V_T}\right) \tag{4.25}$$

Temperature dependence of various BJT parameters has been modeled using the following equations. These equations are used when the BJT temperature is set by setting TEMP parameter.

$$IS(T) = IS \cdot \exp\left(\left(\frac{T}{TNOM} - 1\right) \frac{EG}{N \cdot \phi_T}\right) \cdot \left(\frac{T}{TNOM}\right)^{XTI}$$

(4.26)

$$ISE(T) = ISE \cdot \exp\left(\left(\frac{T}{TNOM} - 1\right) \frac{EG}{NE \cdot \phi_T}\right) \cdot \left(\frac{T}{TNOM}\right)^{XTI/NE}$$

(4.27)

$$ISC(T) = ISC \cdot \exp\left(\left(\frac{T}{TNOM} - 1\right) \frac{EG}{NC \cdot \phi_T}\right) \cdot \left(\frac{T}{TNOM}\right)^{XTI/NC}$$

(4.28)

$$BF(T) = BF \cdot \left(\frac{T}{TNOM}\right)^{XTB}$$

(4.29)

$$BR(T) = BR \cdot \left(\frac{T}{TNOM}\right)^{XTB} \tag{4.30}$$

$$RE(T) = RE + TRE1 \cdot (T - TNOM) + TRE2 \cdot (T - TNOM)^{2}$$

$$(4.31)$$

$$RB(T) = RB + TRB1 \cdot (T - TNOM) + TRB2 \cdot (T - TNOM)^{2}$$

$$(4.32)$$

$$RC(T) = RC + TRC1 \cdot (T - TNOM) + TRC2 \cdot (T - TNOM)^{2}$$

$$(4.33)$$

## 4.3 JFET component

A new line starting with the letter J defines a Junction Field Effect Transistor (JFET). The first string is the component name and the next four strings are names of the nodes connected to the drain, gate, and source of the JFET. The next string is the name of the JFET model. The next number is the JFET area factor.

For example, a JFET of area scaling factor area is instantiated with drain ND, gate NG, and source NS in the following lines. Note, that the model 'njf\_depl' of an n-channel JFET with various hyper-parameters is also written.

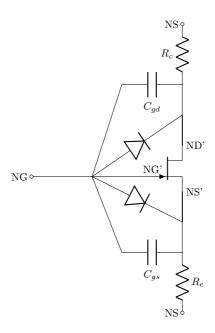

Resistors RD, and RS are added in series with each of the drain, and source, respectively. Junction capacitors CGS and CGD are added in parallel to the 'ideal' diodes present at gate-source and gate-drain junctions, respectively. Together with them, equivalent circuit of the JFET is shown in Fig. 4.3.

Parameters accepted by the 'JFET' component are listed in Table 4.4 together with their meaning, default value, and the unit.

Following equations model an ideal n-channel JFET.

$$V_{ds} = V(ND') - V(NS') (4.34)$$

$$V_{ov} = V(NG') - V(NS') - VTO (4.35)$$

$$I_{ND' \to NS'} = Id + Iii \tag{4.36}$$

$$I_{ND'\to NG'} = Iii \tag{4.37}$$

Figure 4.3: Equivalent circuit of the n-channel JFET component

Table 4.3: Input parameters of the JFET component

| Parameter | Description                                       | Default    | Unit             |

|-----------|---------------------------------------------------|------------|------------------|

| VTO       | threshold voltage                                 | -1.        |                  |

| BETA      | trans-conductance parameter                       | 0          | $A/V^2/r$        |

| LAMBDA    | channel-length modulation                         | 0          | $A/V^2/r$        |

| ALPHA     | G-D junction ionization coefficient               | 0          | $V^{-1}$         |

| VK        | G-D junction ionization voltage                   | 0          | V                |

| ISAT      | leakage current in sub-threshold region           | $10^{-14}$ | A                |

| IS        | G-S, G-D diode saturation current                 | 1          | $A/m^2$          |

| RS        | source series resistance                          | 0          | Ω                |

| RD        | drain series resistance                           | 0          | Ω                |

| N         | G-S, G-D diode emission coefficient               | 1.5        | -                |

| PB        | G-S, G-D junction potential                       | 0.8        | V                |

| CGD       | G-D zero-bias depletion capacitance               | 0          | $F/m^2$          |

| CGS       | G-S zero-bias depletion capacitance               | 0          | $F/m^2$          |

| TT        | transit time                                      | 0          | sec              |

| MJ        | G-D, G-S junction grading coeff.                  | 0.5        | -                |

| FC        | coefficient in forward-bias depletion capacitance | 0.5        | -                |

| TEMP      | JFET temperature                                  | 300        | K                |

| XTI       | IS diode temperature exponent                     | 3.         | -                |

| BETATCE   | trans-conductance temperature coeff.              | 0          | 1/K              |

| VTOTC     | threshold voltage temperature coeff.              | 0          | 1/K              |

| TR1       | RD and RS linear temperature coeff                | 0          | 1/K              |

| TR2       | RD and RS quadratic temperature coeff             | 0          | $1/\mathrm{K}^2$ |

$$Id = \begin{cases} IS \cdot \exp\left(\frac{V_{ov}}{V_T}\right) & \text{if } V_{ov} < 0\\ BETA \cdot V_{ds} \cdot \left(V_{ov} - \frac{1}{2}V_{ds}\right) & \text{if } V_{ov} > V_{ds}\\ \frac{1}{2}BETA \cdot V_{ov}^2 \cdot \left(1 + \lambda(V_{ds} - V_{ov})\right) & \text{if } V_{ov} < V_{ds} \end{cases}$$

$$Ii = \begin{cases} Id \cdot ALPHA \cdot \left(V_{ds} - V_{ov}\right) \cdot \exp\left(-\frac{VK}{V_{ds} - V_{ov}}\right) & \text{if } 0 < V_{ov} < V_{ds}\\ 0 & \text{otherwise} \end{cases}$$

$$(4.39)$$

$$(4.40)$$

Additionally, ideal diodes in Fig. 4.3 represent leakage current at Gate-Drain and Gate-Source junctions. Currents through these diodes are modeled by the following equations.

$$Vgs = V(NG') - V(NS') \tag{4.41}$$

$$I_{gs} = area \cdot IS \cdot \left( \exp\left(\frac{Vgs}{\eta V_T}\right) - 1 \right) + G_{min} \cdot (Vgs)$$

(4.42)

$$Vgd = V(NG') - V(ND') \tag{4.43}$$

$$I_{\rm gd} = area \cdot IS \cdot \left( \exp\left(\frac{Vgd}{\eta V_T}\right) - 1 \right) + G_{min} \cdot (Vgd)$$

(4.44)

Note, that the above equations are valid for n-channel JFET. Polarities of the diodes are reverse in a p-channel JFET.

The semiconductor junction capacitances  $C_{gd}$  and  $C_{gs}$  are modeled as follows.

$$C_{\rm gd} = area \cdot (Cgd1 + Cgd2) \tag{4.45}$$

$$Cgd1 = CGD \cdot \left(1 - \frac{Vd}{PB}\right)^{-M} \tag{4.46}$$

$$Cgd2 = TF \cdot \frac{IS}{\eta V_T} \cdot \exp\left(\frac{Vgd}{\eta V_T}\right) \tag{4.47}$$

$$C_{gs} = area \cdot (Cgs1 + Cgs2) \tag{4.48}$$

$$Cgs1 = CGS \cdot \left(1 - \frac{Vd}{PB}\right)^{-M} \tag{4.49}$$

$$Cgs2 = TF \cdot \frac{IS}{\eta V_T} \cdot \exp\left(\frac{Vgs}{\eta V_T}\right) \tag{4.50}$$

Temperature dependence of various JFET parameters has been modeled using the following equations. These equations are used when the JFET temperature is set by setting TEMP parameter.

$$VTO(T) = VTO + VTOTC \cdot (T - TNOM)$$

$$(4.51)$$

$$BETA(T) = BETA \cdot 1.01^{BETATCE \cdot (T - TNOM)}$$

$$(4.52)$$

$$IS(T) = IS \cdot \exp\left(\left(\frac{T}{TNOM} - 1\right) \frac{EG}{N \cdot \phi_T}\right) \cdot \left(\frac{T}{TNOM}\right)^{XTI}$$

$$(4.53)$$

$$RS(T) = RS + TR1 \cdot (T - TNOM) + TR2 \cdot (T - TNOM)^2$$

$$(4.54)$$

$$RD(T) = RD + TR1 \cdot (T - TNOM) + TR2 \cdot (T - TNOM)^2$$

$$(4.55)$$

In inverted mode, that is,  $V_{\rm ds} < 0$ , source and drain in the normal mode are switched.

# 4.4 MOSFET component

A new line starting with the letter M defines a Metal-Oxide Semi-conductor Field Effect Transistor (MOSFET). The first string is the component name and the next four strings are names of the nodes connected to the drain, gate, source, and substrate of the MOSFET. The next string is the name of the MOSFET model. The next number is the MOSFET area factor.

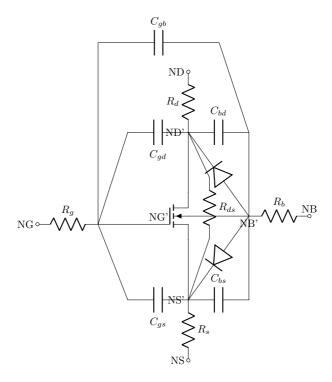

For example, a MOSFET of area scaling factor a is instantiated with drain ND, gate NG, source NS, and substrate NB in the following lines. Note, that the model 'nmos\_depl' of an n-channel MOSFET with various hyperparameters is also written.

.model nmos\_depl NMOS (KP=200u VTO=0.6 PHI=0.6 GAMMA=0)

Figure 4.4: Equivalent circuit of the n-channel MOSFET component

#### Q1 ND NG NS NB nmos\_depl

Resistors RG, RD, RS, and RB are added in series with each of the gate, drain, source, and substrate, respectively. Junction capacitors CBS and CBD are added in parallel to the 'ideal' diodes present at substrate-source and substrate-drain junctions, respectively. Together with them, equivalent circuit of the MOSFET is shown in Fig. 4.4.

Parameters accepted by the 'MOSFET' component are listed in Table 4.4 together with their meaning, default value, and the unit.

Following equations model an ideal n-channel MOSFET.

$$V_{bs} = V(NB') - V(NS') (4.56)$$

Table 4.4: Input parameters of the MOSFET component

| Parameter | Description                                       | Default    | Unit             |

|-----------|---------------------------------------------------|------------|------------------|

| L         | channel length                                    | 1.         | m                |

| W         | channel width                                     | 1.         | m                |

| AS        | Source diffusion area                             | 0.         | $m^2$            |

| AD        | Drain diffusion area                              | 0.         | $m^2$            |

| VTO       | zero-bias threshold voltage                       | 1.         | V/K              |

| KP        | trans-conductance coefficient                     | 0          | $A/V^2/r$        |

| LAMBDA    | channel-length modulation                         | 0          | $A/V^2/r$        |

| GAMMA     | bulk threshold parameter                          | 0          | V                |

| PHI       | surface potential                                 | 0.6        | V                |

| ISAT      | sub-threshold leakage current                     | $10^{-14}$ | $A/m^2$          |

| IS        | G-S, G-D diode saturation current                 | 1          | $A/m^2$          |

| RG        | gate series resistance                            | 0          | Ω                |

| RS        | source series resistance                          | 0          | Ω                |

| RD        | drain series resistance                           | 0          | Ω                |

| RDS       | S-D leakage resistance                            | $10^{9}$   | Ω                |

| RB        | bulk series resistance                            | 0          | Ω                |

| RSH       | D, S diffusion series resistance                  | 0          | $\Omega/m^2$     |

| N         | B-S, B-D diode emission coefficient               | 1.5        | -                |

| PB        | B-S, B-D junction potential                       | 0.8        | V                |

| CBD       | B-D zero-bias depletion capacitance               | 0          | F                |

| CBS       | B-S zero-bias depletion capacitance               | 0          | F                |

| CJ        | bulk planar 0-bias depletion capacitance          | 0          | $F/m^2$          |

| TT        | B-D, B-S diodes transit time                      | 0          | sec              |

| MJ        | B-D, B-S junction grading coeff.                  | 0.5        | -                |

| FC        | coefficient in forward-bias depletion capacitance | 0.5        | -                |

| TEMP      | MOSFET temperature                                | 300        | K                |

| XTI       | IS diode temperature exponent                     | 3.0        | - 1              |

| TCV       | threshold voltage temperature coeff.              | 0          | 1/K              |

| BEX       | mobility temperature exponent.                    | 0          | 1/K              |

| TR1       | RD and RS linear temperature coeff                | 0          | 1/K              |

| TR2       | RD and RS quadratic temperature coeff             | 0          | $1/\mathrm{K}^2$ |

| TRG       | RG linear temperature coeff                       | 0          | 1/K              |

| TRB       | RB linear temperature coeff                       | 0          | 1/K              |

$$V_{ds} = V(ND') - V(NS') \tag{4.57}$$

$$V_{th} = \begin{cases} Vt0 + \gamma \left( \sqrt{2\phi - V_{bs}} - \sqrt{2\phi} \right) & \text{if } V_{bs} < 2\phi. \\ Vt0 & \text{otherwise.} \end{cases}$$

(4.58)

$$V_{ov} = V(NG') - V(NS') - V_{th}$$

(4.59)

$$I_{NS \to ND} = \begin{cases} IS \cdot \exp\left(\frac{V_{ov}}{V_T}\right) & \text{if } V_{ov} < 0\\ KP \cdot \frac{W}{L} \cdot V_{ds} \cdot \left(V_{ov} - \frac{1}{2}V_{ds}\right) & \text{if } V_{ov} > V_{ds}\\ \frac{1}{2}KP \cdot \frac{W}{L} \cdot V_{ov}^2 \cdot \left(1 + \lambda(V_{ds} - V_{ov})\right) & \text{if } V_{ov} < V_{ds} \end{cases}$$

$$\tag{4.60}$$

Additionally, ideal diodes in Fig. 4.4 represent leakage current at Substrate-Drain and Substrate-Source junctions. Currents through these diodes are modeled by the following equations.

$$Vbs = V(NB') - V(NS') \tag{4.61}$$

$$I_{gs} = area \cdot IS \cdot \left( \exp\left(\frac{Vgs}{\eta V_T}\right) - 1 \right) + G_{min} \cdot (Vbs)$$

(4.62)

$$Vbd = V(NB') - V(ND') \tag{4.63}$$

$$I_{\rm gd} = area \cdot IS \cdot \left( \exp\left(\frac{Vgd}{\eta V_T}\right) - 1 \right) + G_{min} \cdot (Vbd)$$

(4.64)

Note, that the above equations are valid for 'n-channel' MOSFET. Polarities of the diodes are reverse in a 'p-channel' MOSFET.

Capacitances at substrate-drain and substrate-source junction  $C_{bd}$  and  $C_{qs}$  are modeled as follows.

$$C_{\rm bd} = area \cdot (Cbd1 + Cbd2) \tag{4.65}$$

$$CBD' = CBD + CJ \cdot AD \tag{4.66}$$

$$Cbd1 = CBD \cdot \left(1 - \frac{Vbd}{PB}\right)^{-MJ} \tag{4.67}$$

$$Cbd2 = TT \cdot \frac{IS}{\eta V_T} \cdot \exp\left(\frac{Vbd}{\eta V_T}\right) \tag{4.68}$$

$$C_{\rm bs} = area \cdot (Cgs1 + Cgs2) \tag{4.69}$$

$$CBS' = CBS + CJ \cdot AS \tag{4.70}$$

$$Cbs1 = CBS' \cdot \left(1 - \frac{Vbs}{PB}\right)^{-MJ} \tag{4.71}$$

$$Cbs2 = TT \cdot \frac{IS}{\eta V_T} \cdot \exp\left(\frac{Vbs}{\eta V_T}\right) \tag{4.72}$$

Capacitances between gate-drain and gate-source nodes are MOS capacitances. They are calculated as follows.

$$C_{gs} = CGSO \cdot W \tag{4.73}$$

$$C_{\rm gd} = CGSO \cdot W \tag{4.74}$$

$$C_{\rm gb} = CGBO \cdot L \tag{4.75}$$

Source and drain series resistances are calculated as follows.

$$R_d = RD + RSH \cdot \frac{AD}{W^2} \tag{4.76}$$

$$R_s = RS + RSH \cdot \frac{AS}{W^2} \tag{4.77}$$

Temperature dependence of various MOSFET parameters has been modeled using the following equations. These equations are used when the MOSFET temperature is set by setting TEMP parameter.

$$VTO(T) = VTO + TCV \cdot (T - TNOM)$$

$$(4.78)$$

$$KP(T) = KP \cdot \left(\frac{T}{TNOM}\right)^{BEX}$$

$$(4.79)$$

$$IS(T) = IS \cdot \exp\left(\left(\frac{T}{TNOM} - 1\right) \frac{EG}{N \cdot \phi_T}\right) \cdot \left(\frac{T}{TNOM}\right)^{XTI/N}$$

$$(4.80)$$

$$RS(T) = RS + TR1 \cdot (T - TNOM) + TR2 \cdot (T - TNOM)^2$$

$$(4.81)$$

$$RD(T) = RD + TR1 \cdot (T - TNOM) + TR2 \cdot (T - TNOM)^2$$

$$(4.82)$$

$$RB(T) = RB + TRB \cdot (T - TNOM)$$

$$(4.83)$$

$$RG(T) = RG + TRG \cdot (T - TNOM)$$

$$(4.84)$$

In inverted mode, that is,  $V_{\rm ds} < 0$ , source and drain in the normal mode are switched.

### 4.5 MESFET component

A new line starting with the letter Z defines a Metal-Semiconductor Field Effect Transistor (MESFET). The first string is the component name and the next four strings are names of the nodes connected to the drain, gate, and source of the MESFET. The next string is the name of the MESFET model. The next number is the MESFET area factor.

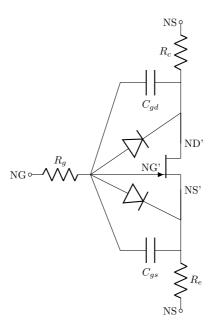

For example, a MESFET of area scaling factor area is instantiated with drain ND, gate NG, and source NS in the following lines. Note, that the model 'mesfet\_depl' of an n-channel MESFET with various hyper-parameters is also written.

.model mesfet\_depl MESFET (KP=200u VTO=0.6 PHI=0.6 GAMMA=0)

Z1 ND NG NS mesfet depl

Resistors RD, RG, and RS are added in series with each of the drain, gate, and source, respectively. Junction capacitors CGS and CGD are added in parallel to the 'ideal' diodes present at gate-source and gate-drain junctions, respectively. Together with them, equivalent circuit of the MESFET is shown in Fig. 4.5.

Parameters accepted by the 'MESFET' component are listed in Table 4.5 together with their meaning, default value, and the unit.

Following equations model an ideal n-channel MESFET.

$$V_{ds} = V(ND') - V(NS') (4.85)$$

$$V_{ov} = V(NG') - V(NS') - VTO (4.86)$$

$$I_{ND'\to NS'} = Id (4.87)$$

Figure 4.5: Equivalent circuit of the MESFET component

Table 4.5: Input parameters of the MESFET component

| Parameter | Description                                       | Default    | Uni     |

|-----------|---------------------------------------------------|------------|---------|

| VTO       | threshold voltage                                 | -1.        |         |

| BETA      | trans-conductance parameter                       | 0          | $A/V^2$ |

| ALPHA     | saturation voltage parameter                      | 2          | $A/V^2$ |

| LAMBDA    | channel-length modulation                         | 0          | $A/V^2$ |

| VBD       | G-D, G-S junction breakdown voltage               | 100        | V       |

| ISAT      | leakage current in sub-threshold region           | $10^{-14}$ | A       |

| IS        | G-S, G-D diode saturation current                 | 1          | A/m     |

| RS        | source series resistance                          | 0          | Ω       |

| RG        | gate series resistance                            | 0          | Ω       |

| RD        | drain series resistance                           | 0          | Ω       |

| N         | G-S, G-D diode emission coefficient               | 1.5        | -       |

| В         | Gdoping tail extension parameter                  | 2          | -       |

| PB        | G-S, G-D junction potential                       | 0.8        | V       |

| CDS       | D-S capacitance                                   | 0          | F/m     |

| CGD       | G-D zero-bias depletion capacitance               | 0          | F/m     |

| CGS       | G-S zero-bias depletion capacitance               | 0          | F/m     |

| TT        | transit time                                      | 0          | sec     |

| MJ        | G-D, G-S junction grading coeff.                  | 0.5        | -       |

| FC        | coefficient in forward-bias depletion capacitance | 0.5        | -       |

| TEMP      | MESFET temperature                                | 300        | K       |

| XTI       | IS diode temperature exponent                     | 3.         | -       |

| BETATCE   | trans-conductance temperature coeff.              | 0          | 1/K     |

| VTOTC     | threshold voltage temperature coeff.              | 0          | 1/K     |

| TRD1      | RD linear temperature coeff                       | 0          | 1/K     |

| TRG1      | RG linear temperature coeff                       | 0          | 1/K     |

| TRS1      | RS linear temperature coeff                       | 0          | 1/K     |

$$Id = \begin{cases} IS \cdot \exp\left(\frac{V_{ov}}{V_T}\right) & \text{if } V_{ov} < 0 \text{ or } \alpha < 0 \\ \frac{\beta \cdot V_{ov}^2}{1 + B \cdot V_{ov}} \cdot (1 + \lambda V_{ds}) \cdot (1 - (1 - \frac{\alpha V_{ds}}{3})^3) & \text{if } 0 < V_{ds} < 3/\alpha \\ \frac{\beta \cdot V_{ov}^2}{1 + B \cdot V_{ov}} \cdot (1 + \lambda V_{ds}) & \text{if } V_{ds} > 3/\alpha \end{cases}$$

$$(4.88)$$

$$(4.89)$$

Additionally, ideal diodes in Fig. 4.3 represent leakage current at Gate-Drain and Gate-Source junctions. Currents through these diodes are modeled by the following equations.

$$Vgs = V(NG') - V(NS') \tag{4.90}$$

$$I_{gs} = area \cdot IS \cdot \left( \exp\left(\frac{Vgs}{\eta V_T}\right) - 1 \right) + G_{min} \cdot (Vgs)$$

(4.91)

$$Vgd = V(NG') - V(ND') \tag{4.92}$$

$$I_{\rm gd} = area \cdot IS \cdot \left( \exp\left(\frac{Vgd}{\eta V_T}\right) - 1 \right) + G_{min} \cdot (Vgd)$$

(4.93)

Note, that the above equations are valid for n-channel MESFET. Currently, the simulator supports *only* n-channel MESFET.

The semiconductor junction capacitances  $C_{gd}$  and  $C_{gs}$  are modeled as follows.

$$C_{\rm gd} = area \cdot (Cgd1 + Cgd2) \tag{4.94}$$

$$Cgd1 = CGD \cdot \left(1 - \frac{Vd}{PB}\right)^{-M} \tag{4.95}$$

$$Cgd2 = TT \cdot \frac{IS}{\eta V_T} \cdot \exp\left(\frac{Vgd}{\eta V_T}\right) \tag{4.96}$$

$$C_{\rm gs} = area \cdot (Cgs1 + Cgs2) \tag{4.97}$$

$$Cgs1 = CGS \cdot \left(1 - \frac{Vd}{PB}\right)^{-M} \tag{4.98}$$

$$Cgs2 = TT \cdot \frac{IS}{\eta V_T} \cdot \exp\left(\frac{Vgs}{\eta V_T}\right) \tag{4.99}$$

Temperature dependence of various MESFET parameters has been modeled using the following equations. These equations are used when the MESFET temperature is set by setting TEMP parameter.

$$VTO(T) = VTO + VTOTC \cdot (T - TNOM) \quad (4.100)$$

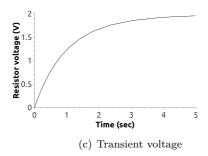

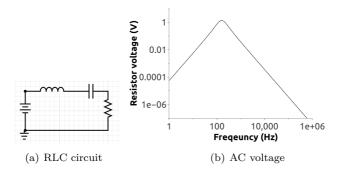

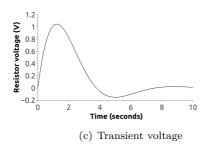

$$BETA(T) = \beta \cdot 1.01^{BETATCE \cdot (T - TNOM)} \quad (4.101)$$